Some codes and projects related to the Compiler Design, Digital System Design, Assembly and microprocessor, Operating Systems courses, Digital Logic Circuit Design, Programming Language Design

Designing and implementation of:

- A Simple Python-based compiler (The principles of Compiler Design)

- Round Robin time scheduling algorithm (Operating Systems)

- The assembly language implementation of a banking system (Microprocessors and Assembly language)

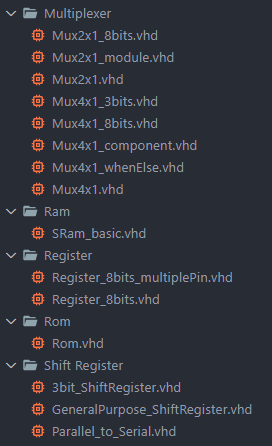

- VHDL codes of diffrent parts of a basic computer (Digital Systems Design)

- A BCD to 7 Segment Decoder (Digital Logic Circuit Design)

- A comparison among Python, Cython, and the C languages (Programming Language Design)

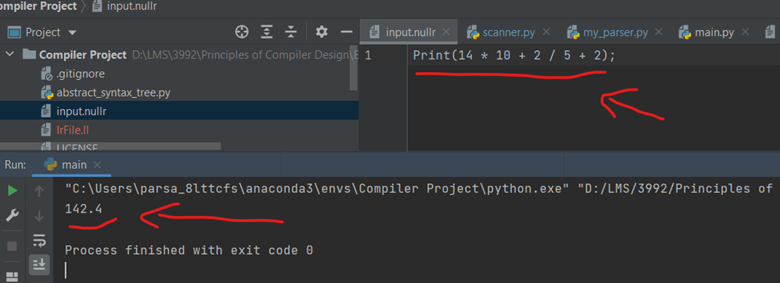

A Simple Python-based compiler

- Github repo

A Simple Python-based compiler, using RPLY package, for my own made-up language

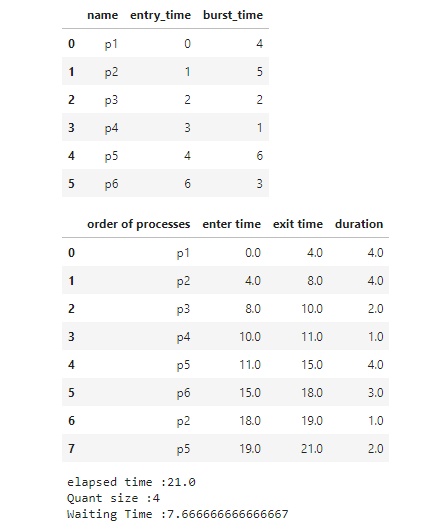

Round Robin time scheduling algorithm

- Github repo

Overview

Round robin scheduling is a pre-emptive algorithm commonly used in operating systems to schedule processes.

In round robin scheduling, the CPU is assigned to each process in a queue turn by turn for a time period. Once the time is over, the process is moved to the end of the queue and the CPU is shifted to the next process in the queue. In this manner, processes are handled from a cyclic queue until the burst time of a process has passed.

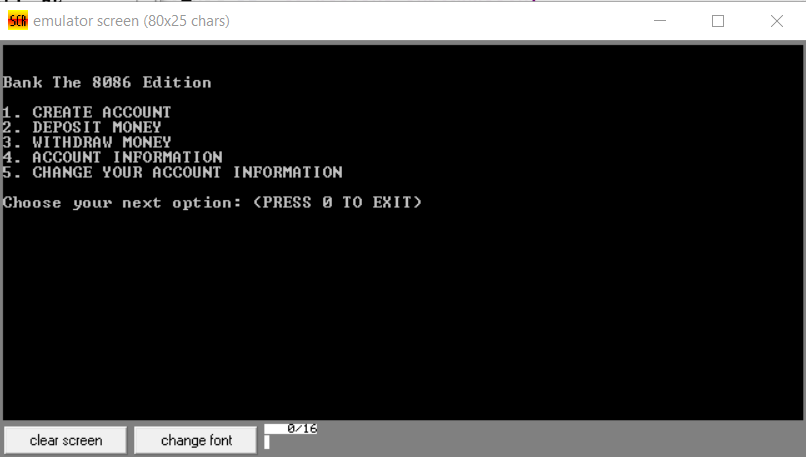

The assembly language implementation of a banking system

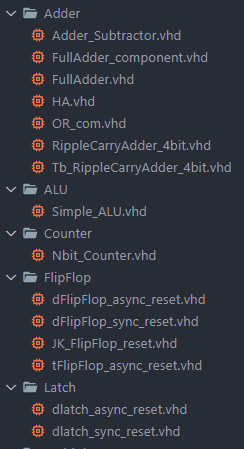

VHDL codes regarding the Digital Systems Design course

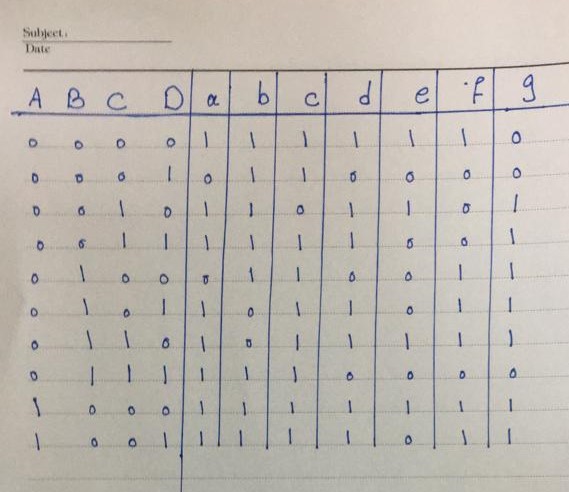

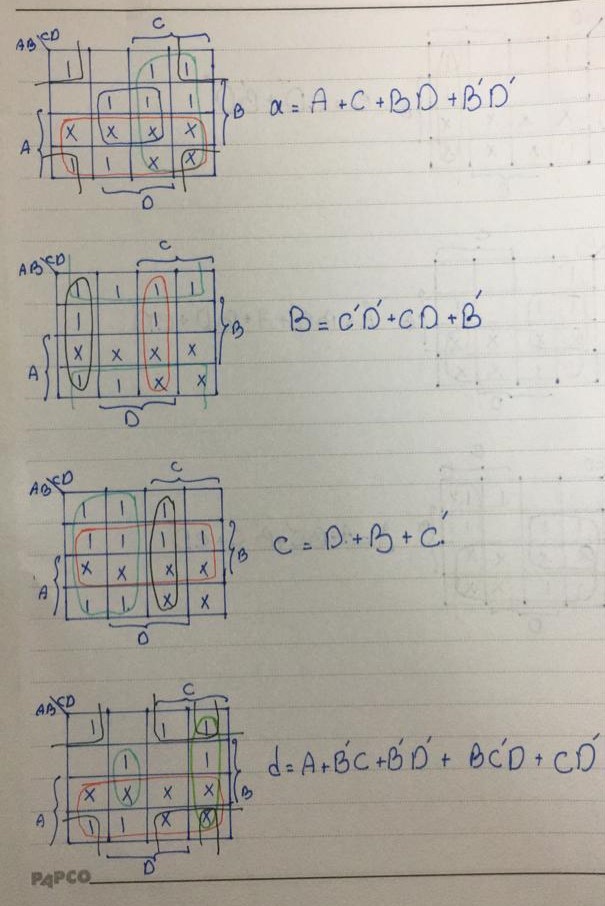

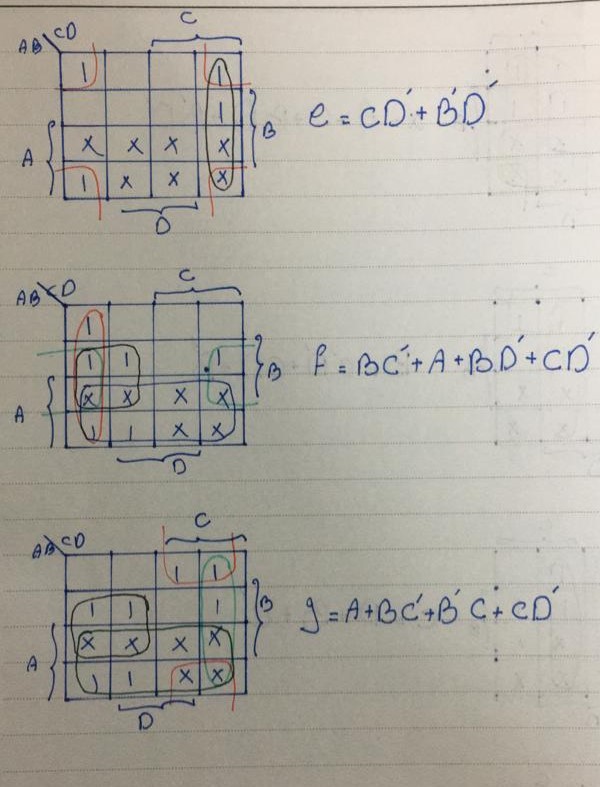

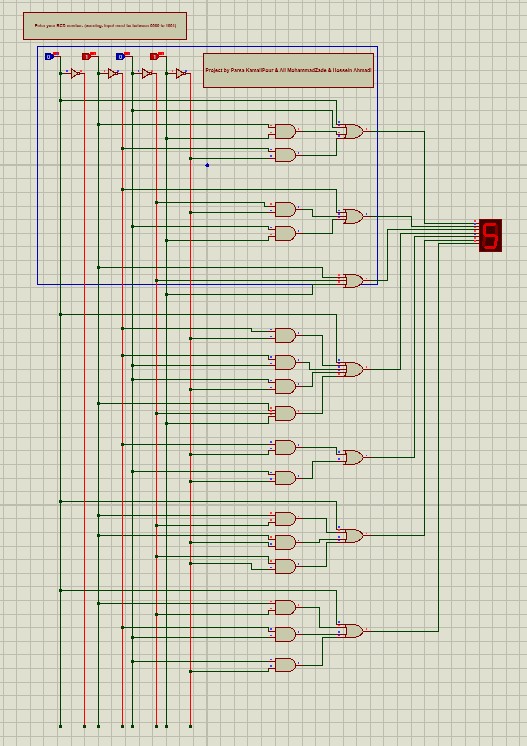

A BCD to 7 Segment Decoder (Digital Logic Circuit Design)

Design a Decoder that translate a BCD number to a decimal number and shows it on a 7 Segment.

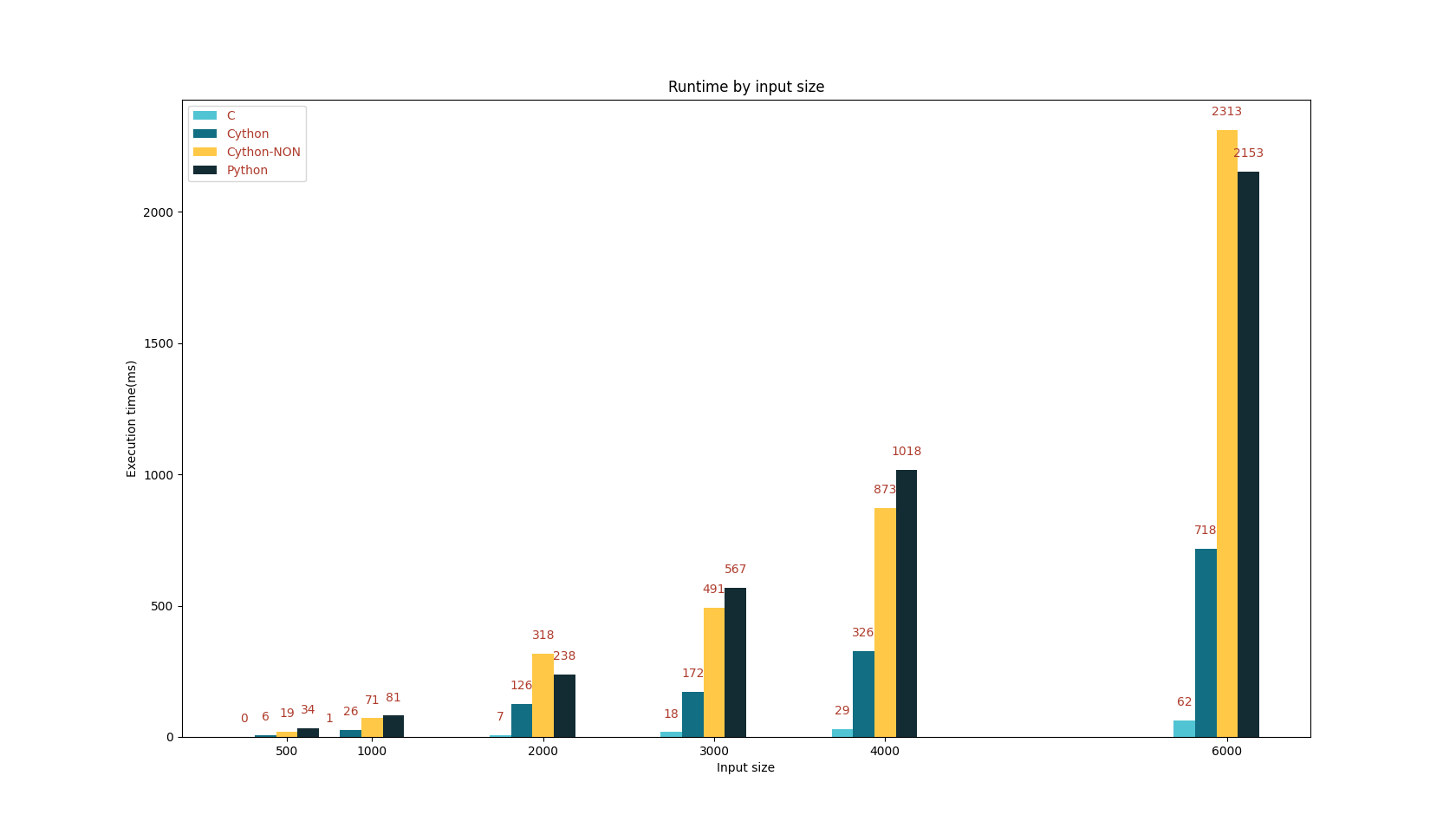

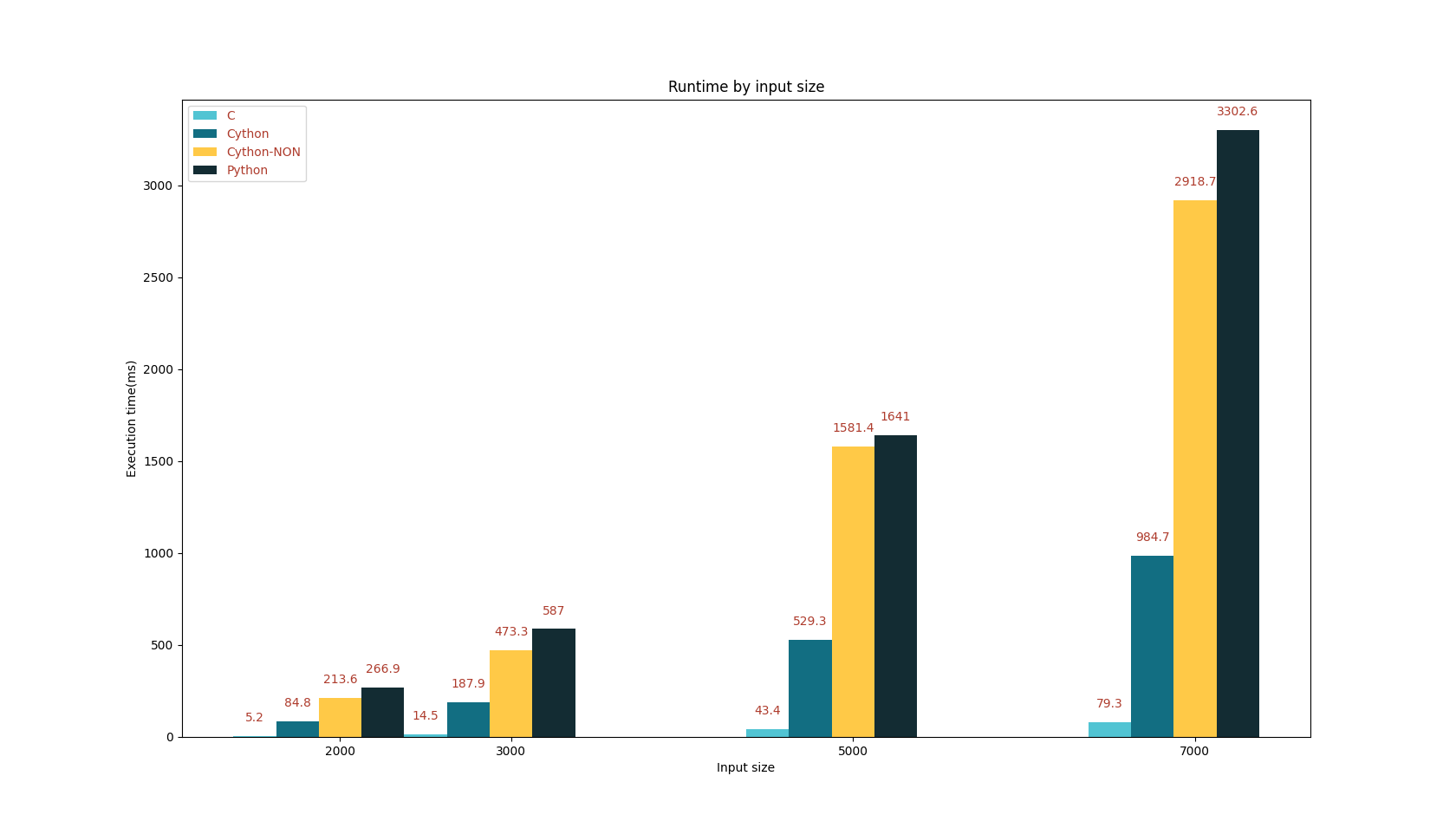

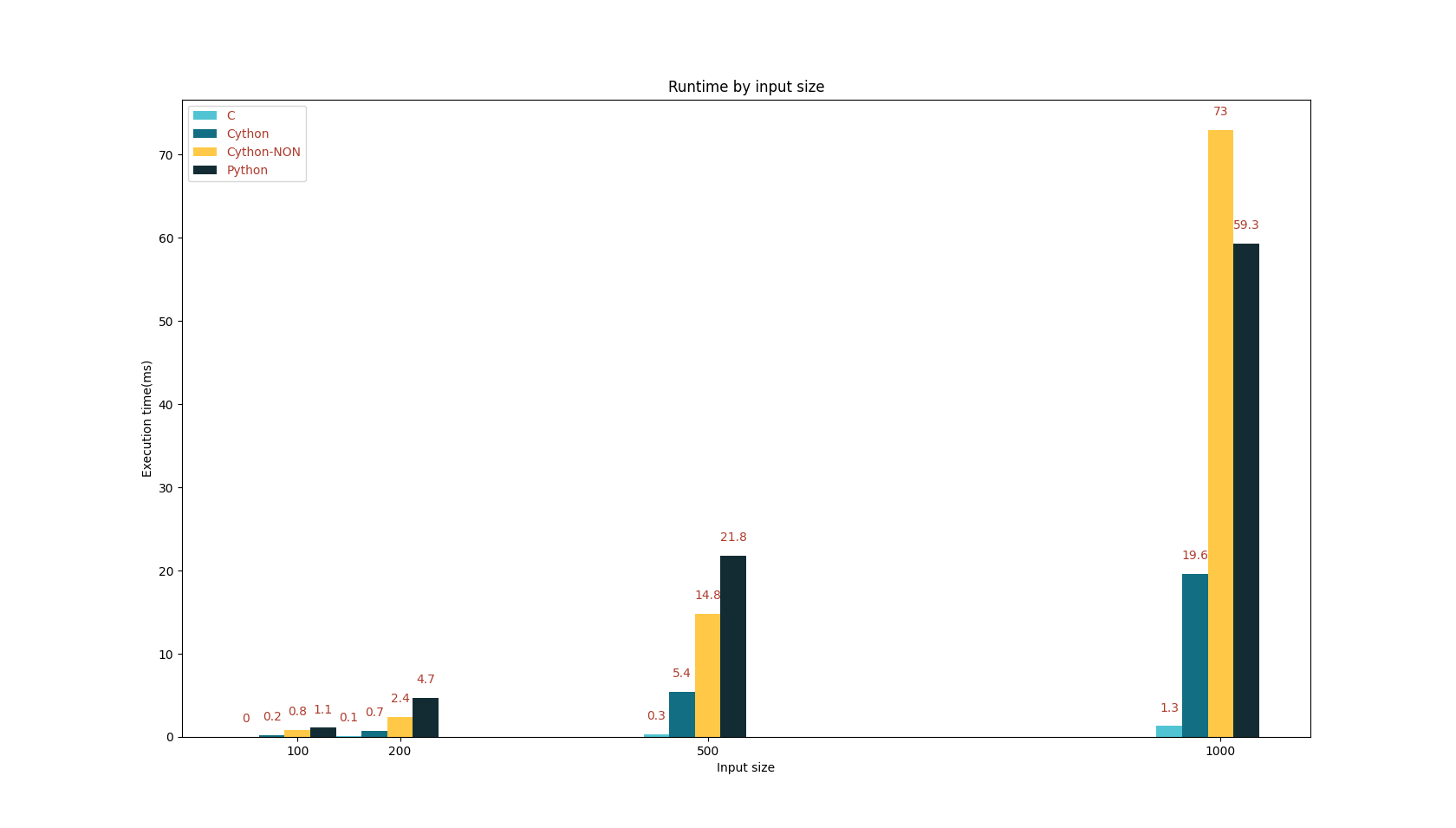

A comparison among Python, Cython, and the C languages (Programming Language Design)

- Github repo

In this project, we are comparing the execution time of four different approaches, including :

- Pure C

- Optimized Cython

- Non-Optimized Cython

- Pure Python